在行业不断喊出“摩尔定律已死!”的当下,依旧有人在不断埋头推进芯片工艺,以超人的先进的技术挑战那些难如登天的任务。在7nm芯片量产的当下,5nm的

摩尔定律的定义为:“当价格不变时,集成电路上可容纳的元器件的数量约每隔18-24个月便会增加一倍,性能也将提升一倍。”

也就是说,在一年半到两年的时间里,你用同样价钱能够买到的电脑手机/其他电子科技类产品性能理论上能增加一倍。

于是,就是这么两行简单的描述,在过去50年时间里推动着全美国——甚至全世界——的经济快速地发展,直接催生了二战后结束后美国科技产业的全方面爆发,至今仍旧引领全球。如今全球科学技术殿堂“美国硅谷”中的“硅”字,就是源自于集成电路的主要原材料——硅。

一块面积不变的芯片上,若需要容纳比以前多一倍的元器件数量,那么就需要这些元器件(一般是晶体管)体积更小,同时排布得更“紧”——我们常说的10nm、7nm芯片制程就是用来描述晶体管栅极宽度大小的。纳米进程数字越小,芯片能容纳的晶体管数量就越多、性能就越强大。

跟牛顿第二定律这种基本物理学定律不同,摩尔定律并不是一个真正的科学定理,它只是描述了芯片技术快速地发展的现状。芯片的性能不会自动增长,真正推动摩尔定律往前发展的是那些不断砸钱、招人、实验、研发的芯片企业们。

不过,市场与经济同样有周期,摩尔定律也不例外。随着芯片工艺越来越逼近硅的物理极限,摩尔定律在最近这几年来发展速度不断变慢,每一代芯片工艺的研发成本也像滚雪球一样疯狂飙升——比如台积电宣布砸250亿美元研发5nm工艺——随技术红利不断消失,往牌桌上砸钱的玩家也慢慢变得少。

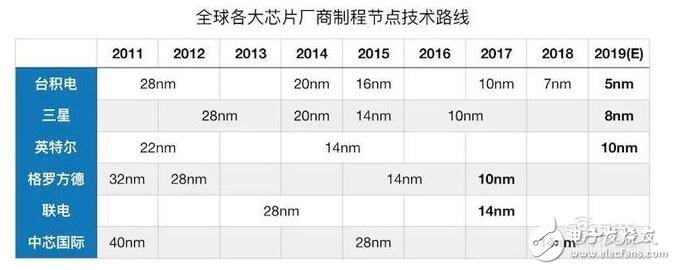

2018年8月28日,全球第二大芯片代工厂格罗方德宣布,它将无限期地暂停7nm芯片工艺的开发,以便将资源转移到14nm和12nm工艺上。

同样在2018年8月,全球第三大芯片代工厂联电宣布,不再投资12nm以下的先进芯片制程。

于是,从智能手机到个人电脑、从云计算比特币挖矿,全球无数个依靠摩尔定律红利进行不断研发创新的企业猛一抬头,忽然现在市面上还在哼哧哼哧埋头推动摩尔定律的人,就只剩台积电、英特尔三星这三个“老冤家”了。

他们一个是全球第一大芯片代工厂(台积电),另外两个则是全球芯片IDM厂商的老大和老二(英特尔和三星)。

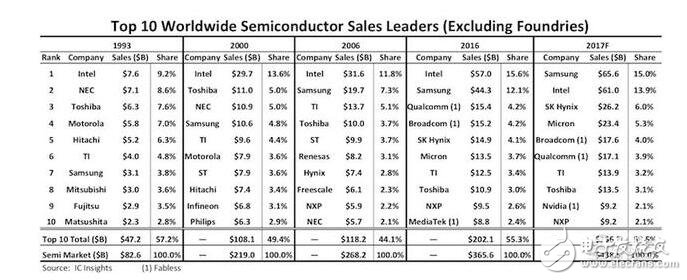

三星的半导体业务由来已久,早在1993年,三星就已经成功跻身全球第七大半导体厂商之位,在此后的二十多年里一路稳中有进,从未跌出过全球前十。去年10月,三星电子宣布通过了8nm LPP工艺验证,但一直到2018年11月才在自家年度旗舰手机芯片Exynos 9820手上用上8nm技术,预计2019年初量产。

▲ICInsights机构发布的1993-2017F全球半导体十大厂商变迁图,20多年里英特尔始终稳坐第一

至于老牌芯片巨头英特尔则更是在先进芯片工艺上投入重大,早年间英特尔在半导体领域几乎一骑绝尘,连台积电都要仰仗英特尔的给予代工认证(1988年)。而从1999年的180nm工艺开始,英特尔以每两年更新一代的节奏研发先进制造工艺,在过去20多年里坐稳了全球第一大半导体厂商的龙头宝座。直到2017年,三星凭借内存价格暴涨才超越英特尔,翻身跃居第一。

英特尔的工艺研发进程在近年来受到了不小的挑战,在2015年7月,英特尔宣布本该在2016年面世的10nm工艺推迟量产,此后英特尔虽然也在一直在优化14nm技术,部分10nm芯片也开始小批量出货,但其10nm至今还没正式公开宣布量产。

不过话说回来,早期的nm制程=栅极宽度大小,但是后期延伸出了更多让晶体管紧凑的方法,因此nm制程与栅极宽度大小并不一一对应,取决于各家定义:比如英特尔14nm的栅极宽度为42nm,同期三星14nm的栅极宽度为48nm,而台积电16nm的栅极宽度为45nm。在1um^2的面积上,英特尔14nm晶体管可以摆上101个,三星14nm晶体管只能摆75个,台积电的16nm晶体管能摆上81个。

但无论怎么算,目前台积电在先进工艺上处于大幅领先的位置,其7nm芯片已经量产并陆续接下苹果A12、华为麒麟980、高通骁龙855、比特大陆、嘉楠耘智订单。台积电也常年称霸芯片代工领域老大地位,目前市占率超过56%(第二名为9%)。

去年,台积电已经吹响了5nm工艺制程的冲锋号角。2018年1月,台积电在***开设了新的5nm晶圆18厂。同年6月的半导体技术论坛上,台积电宣布投资250亿美元研发、生产5nm工艺。

而在年底的台积电年度“供应链管理论坛”上,台积电总裁魏哲家表示,该5nm晶圆厂目前已经在设备装机中,预计2019年Q1完工,2019年Q2将进行5nm芯片制程的风险试产,2020年投入量产。

其实,除了台积电之外整个芯片制造业在推进10nm以下技术的研发都多少遇到了些问题,但这个“锅”并不完全要他们自己背,上游设备商也要背一部分。

芯片制造的环节很复杂,首先要对硅进行冶炼提纯切割等,得到一块大的硅晶圆。

紧接着,晶圆要经过湿洗(去除杂质)、光刻(雕刻出芯片图案)、离子注入(形成场效应管)、刻蚀(吹走/洗走多余的材料)、冲洗、退火、氧化、气相淀积等众多环节,最后通过测试才送去切割成无数小片片,经过封装后变成我们熟悉的芯片。

如果再进一步简化,就可以看作是:用***往硅片上雕刻出特定图案,用刻蚀机吹走/洗走多余的材料,最后经过一系列处理成为芯片。

以上每一个环节都会涉及到专用的制造设备。由于芯片工艺制程的逐步发展,这些芯片图案的线条也慢慢变得细,对于设备的要求也慢慢变得高——首当其冲的,自然是负责“雕刻”的***了。

***的运作原理是:先把设计好的芯片图案印在掩膜上,接着用激光光束穿过印着图案的掩膜和光学镜片,将芯片图案曝光在带有光刻胶涂层的硅片上,此时涂层被光照到的地方发生反应溶解,没有被照到的地方保持不变,掩膜上的图案就被转移到芯片光刻胶涂层上。

刻蚀相对光刻要容易。刻蚀机通过干刻蚀(用等离子体进行薄膜刻蚀)及湿蚀刻(液体腐蚀)的方法,根据印上去的图案刻蚀掉有图案(或者没有图案)的部分,留下剩余的部分,芯片图案又从光刻胶涂层转移到了硅片上。

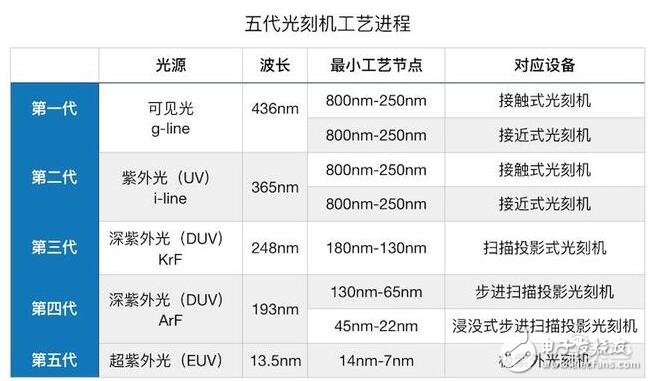

目前市面上高端芯片使用的普遍是第四代DUV深紫外***,它的激光波长是193nm(波长越小,“刻刀”越精密),它的理论“雕刻”极限大约是130nm。

然而到了2005年,***厂商还是没能成功量产下一代波长更短、“刻刀”更精密的第五代EUV超紫外***,逼得近年来各大芯片制造厂不断发明创新,用上了多重曝光、步进式扫描、浸润式光刻等更多新技术,继续维持摩尔定律从90nm到如今的14nm、10nm发展。而浸润式光刻技术的开创者林本坚博士也获得了2018年未来科学大奖-数学与计算机科学奖。

用193nm的DUV深紫外***造7nm芯片,就像用一支直径是193nm的笔去写7nm的字一样,其难度不亚于拉着骆驼穿过针眼,半导体技术发展到最后竟然有点哲学的意思。

而且,由于频繁用上了浸润式光刻、三重曝光等复杂技术,用193nm DUV***打造7nm芯片的成本已然超过了EUV ,生产交期更长、技术更复杂,因此7nm之后,行业对于第五代EUV超紫外***的呼声越来越强烈。

EUV超紫外***的激光波长只有13.5nm,是一把非常精细的“雕刻刀”。这一技术源自于美国雷根时代的“星战计划”。EUV超紫外***本应在2005年就量产上阵,然而由于这一技术的研发难度巨大,EUV设备不仅所需的光源功率迟迟无法达到250W工作功率需求,而且对于光学透镜、反射镜系统的精密度高到变态。

比如EUV***的关键部件反射镜,其瑕疵大小只能以pm(nm的千分之一)计。如果反射镜面积有整个德国大,最高的突起处不能高于一厘米。

“如果我们交不出EUV超紫外***的话,摩尔定律就会从此停止。”荷兰***巨头ASML总裁暨CEO温彼得(Peter Wennink)曾经这样说。

因此,虽然英特尔、台积电、三星这三大个老冤家彼此抢订单、抢人才的竞争不断,但是在2012年的时候,他们三个曾经联袂向荷兰ASML***厂投资41亿、14亿、9.75 亿美元,督促ASML加快研发新一代EUV超紫外***,可见***的重要性。

虽然荷兰ASML的EUV***跳票了十多年(并且业内老二、老三尼康与佳能纷纷放弃研发,这个节奏是否很眼熟?),但到了2016年,ASML终于将EUV***造了出来并成功量产。

2017年,ASML出货了11台EUV***,2018年出货了18台。虽然这些EUV***基本上被台积电、三星这些厂商优先买去了,但中芯国际也出资1亿多美金购买了一台7nm工艺EUV***,预计2019年上半年到货。

ASML表示,由于EUV超紫外***的零组件多达5万多个部件,从客户下单到正式交货,交期约21个月。

目前台积电已经量产的华为、苹果、比特大陆等7nm芯片都还是基于193nm的DUV深紫外***的,但是DUV技术已逼近极限,再往下走的线nm芯片的技术路径必须转到EUV。

2018年10月,台积电宣布基于EUV技术的7nm芯片已经流片成功,和7nm DUV相比,7nm EUV能大大的提升芯片密度20%,功耗降低6%至12%。台积电的5nm有望大面积用上EUV。

在先进工艺上的不断砸钱研发也给予了台积电丰厚的产业回报,常年称霸芯片代工领域老大地位的台积电,这两年靠着苹果、高通、华为等的订单赚得盆满钵满,其2018年前三季度合并营收达新台币7417.03亿元,较2017年同期增长6.0%,8月初的病毒事件都未曾大面积影响其财报。

上文提到,台积电在2018年1月就开始兴建5nm晶圆厂了;除了钱、晶圆厂、***之外,5nm的刻蚀机、EDA工具、客户等也已经陆续就位:

芯片的制作的完整过程可以简化成用***“雕刻”图案,用刻蚀机吹走/洗走多余的材料。相对于***,刻蚀机的研发难度要小一些,但刻蚀机也是除***以外最关键的设备。目前一台刻蚀机单价在200万美元左右,一个晶圆厂需要40-50台刻蚀机。

国外刻蚀机设备厂商主要有应用材料(Applied Materials)、科林研发(LAM) 、东京威力科创(TEL)、日立先端(Hitach)、牛津仪器等;国内玩家则有中微半导体、北方微电子、金盛微纳科技,我们跟国外的差距没有***那么大。

2018年12月,中微半导体的5nm等离子体刻蚀机也宣布通过台积电验证,将用于全球首条5nm制程生产线nm时代,中微半导体的刻蚀机也进入了台积电的7nm产线nm EDA工具已就位;

目前,全球几大EDA巨头都已经陆续推出了5nm芯片设计工具,比如在2018年10月,新思科技宣布其数字和定制设计平台通过了台积电的5nm EUV工艺技术认证。

CEO陈立武曾经告诉智东西,目前Cadence已经和很多合作伙伴开始了7nm、5nm、甚至3nm芯片工艺制程的研究。比如今年年初,比利时公司Imec与Cadence就成功流片了首款3nm测试芯片。陈立武说,现在5nm市场是最活跃的,有很多非常积极的公司正在安排5nm相关EDA软件与设计、IP的协同。

有工艺,自然也需要有市场。台积电曾表示,目前很多客户慢慢的开始基于新工艺开发芯片了。

不过由于芯片设计的复杂度不同,像比特大陆这种专用芯片设计起来相对容易、手机芯片次之、电脑芯片与数据

在再次之,所以最先用上先进的工艺的往往是专用芯片而非通用芯片,比如台积电7nm的头批客户只包含了比特币与手机芯片玩家。而根据华为

平台与关键技术开发部部长夏禹此前给出的芯片工艺路线nm芯片研发进程,预计5nm芯片问世的时间点在2020年。华为研发人员曾经告诉智东西,在7nm时代,华为和台积电合作研发了3年,耗资3亿美元,才终于在2018年拿出7nm芯片设计。

工艺越先进,需要投入的也成本越高,这一个道理在芯片代工厂跟芯片设计商同理,5nm的设计总成本(人工与许可费)是7nm的1.5倍左右。

而根据台积电数据,基于5nm工艺生产的A72芯片,芯片面积缩小了1.8倍,速度提升了14.7% -17.1%。

在PC和手机的出货量开始走下坡路的当下,不少机构对于今年全球半导体市场的走势持悲观态度。不过,

5G、数据中心这些高端芯片需求正处在持续上升之势,虽然目前台积电暂时领先,但是英特尔、三星、台积电三大巨头的竞争还将持续,市场对先进工艺的热情依旧持续。与此同时,三星和台积电都已经公布了3nm的线nm是一个难关的话,受到量子隧穿效应影响的3nm就更是一个逼近物理极限的重要挑战。摩尔定律尚未完结,只是门槛越来越高了。

营收飙涨,毛利率高达57.8% /

电位于美国亚利桑那州菲尼克斯附近的Fab 21工厂的第二大知名客户,该工厂慢慢的开始试产包括N

制程技术的出货高潮,预示着其在半导体制造领域的领头羊进一步巩固。随着苹果iPhone 16系列新机发布,预计搭载的A18系列处理器将采用

在近日举办的IEEE 国际电子器件会议(IEDM)的小组研讨会上透露,其1.4

基于 S32M276 集成解决方案 专为汽车和 PMSM 电机控制应用而设计

GCC Runtime替代品GNUstep Objective-C Runtime

《算力芯片 高性能 CPU/GPU/NPU 微架构分析》第1-4章阅读心得——算力之巅:从基准测试到CPU微架构的深度探索

摩尔斯微电子推出社区论坛与开源GitHub资源库,新资源的上线将加速全球工程师与开发者的Wi-Fi开发进程

STC32G8K64 单片机 的P00(ADC8)脚短路到GND 会死机,如何来解决?